Quickdev16 Windows Driver

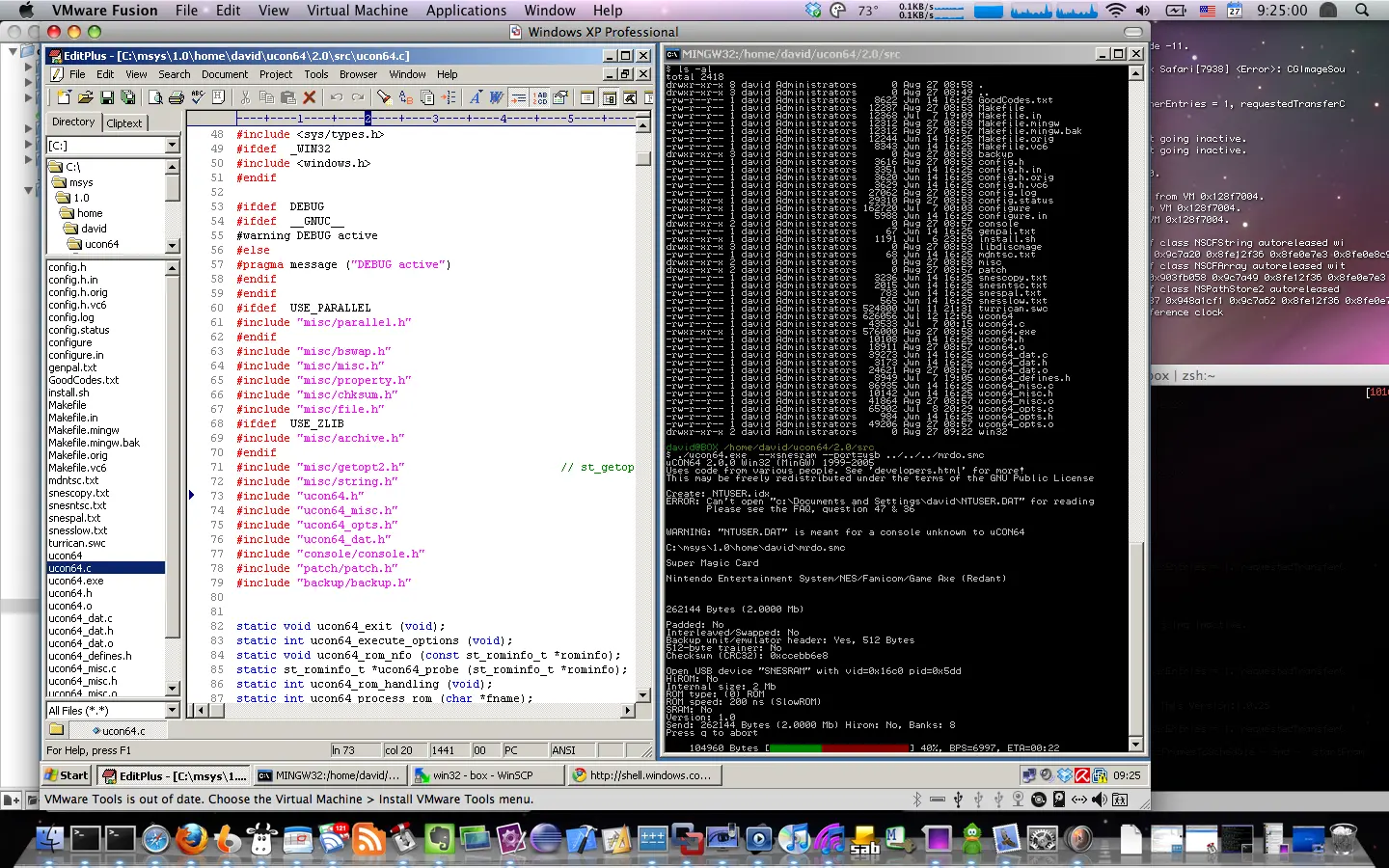

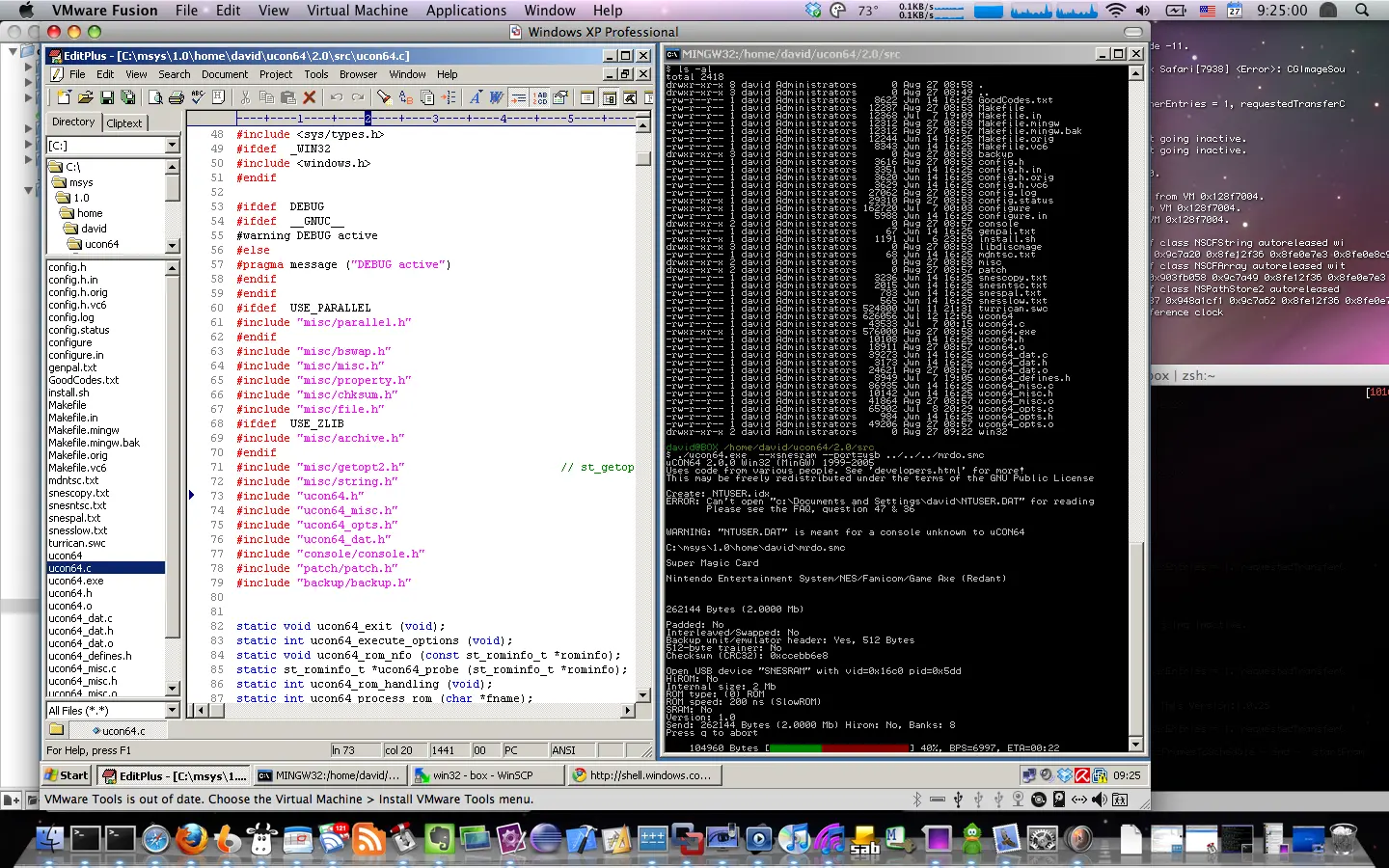

Created a binary for windows using minGW and libusb. So i can confirm that quickdev16 will work under Windows.

Quickdev16 Windows Driver Read More »

Avr

Created a binary for windows using minGW and libusb. So i can confirm that quickdev16 will work under Windows.

Quickdev16 Windows Driver Read More »